服務熱線

深圳線下交流來了產(chǎn)業(yè)大咖,分享了臺積電的CoWoS干貨。

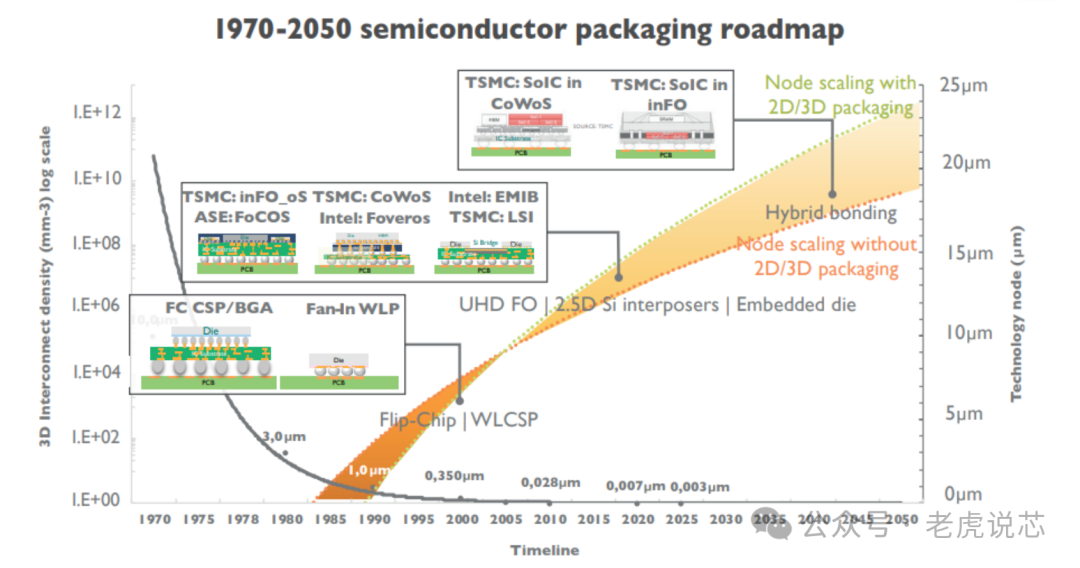

臺積電的CoWoS(Chip On Wafer On Substrate)技術是一種先進的半導體封裝技術,旨在提升集成電路的性能、減小封裝尺寸,并有效降低功耗。

CoWoS技術通過在一個硅中介層(Interposer)上集成多個芯片(或芯片組),形成一個高性能的封裝解決方案。該技術主要應用于需要高帶寬和低延遲的高性能計算(HPC)、人工智能(AI)加速器和數(shù)據(jù)中心等領域。

1、CoWoS的關鍵技術點

多芯片集成:CoWoS技術能夠將不同功能的芯片(如CPU、GPU、內(nèi)存芯片等)集成到一個封裝中。這些芯片可以采用不同的制造工藝節(jié)點,從而實現(xiàn)最佳的性能和成本效益組合。

硅中介層(Interposer):硅中介層是CoWoS技術的核心組件,提供了高密度的互連網(wǎng)絡。中介層上的微米級金屬線和通孔(TSV,Through-Silicon Via)實現(xiàn)了芯片間的高速數(shù)據(jù)傳輸。

高效散熱:多芯片集成的封裝需要有效的散熱管理,CoWoS技術通過優(yōu)化的封裝設計和材料選擇,實現(xiàn)了高效的散熱,從而確保芯片在高負載下穩(wěn)定運行。

根據(jù)采用的不同的中介層( interposer ), 臺積電把CoWoS 封裝技術分為三種類型——CoWoS-S(Silicon Interposer)、CoWoS-R(RDL Interposer)以及CoWoS-L(Local Silicon Interconnect and RDL Interposer)。

2、技術優(yōu)勢

提升帶寬和性能:通過減少芯片之間的互連距離,CoWoS技術顯著提高了數(shù)據(jù)傳輸帶寬和速度,降低了延遲。適用于需要快速數(shù)據(jù)處理和高吞吐量的應用場景。

功耗優(yōu)化:緊密的芯片集成和高效的互連設計降低了系統(tǒng)的整體功耗,延長了設備的使用壽命。

靈活的設計和制造:CoWoS技術支持不同工藝節(jié)點和不同類型芯片的集成,設計靈活性大。可以根據(jù)具體需求進行定制化設計,滿足多樣化的市場需求。

3、應用領域

高性能計算(HPC):需要處理大量數(shù)據(jù)和復雜計算的領域,如科學計算、金融建模等。

人工智能(AI):AI加速器和深度學習處理器需要高帶寬和低延遲的數(shù)據(jù)傳輸。

數(shù)據(jù)中心:服務器和網(wǎng)絡處理器等需要高效的數(shù)據(jù)處理能力和快速的存儲訪問。

小結:臺積電的CoWoS(Chip On Wafer On Substrate)技術通過將多個芯片緊密集成在一個封裝中,并利用硅中介層提供高速互連,顯著提升了系統(tǒng)的性能、帶寬和能效,適用于需要高性能和高帶寬的計算和數(shù)據(jù)處理應用。

免責聲明:本文采摘自“老虎說芯”,本文僅代表作者個人觀點,不代表薩科微及行業(yè)觀點,只為轉載與分享,支持保護知識產(chǎn)權,轉載請注明原出處及作者,如有侵權請聯(lián)系我們刪除。

粵公網(wǎng)安備44030002007346號

粵公網(wǎng)安備44030002007346號